Mae tyfu haen ychwanegol o atomau silicon ar swbstrad wafer silicon yn cynnig sawl mantais:

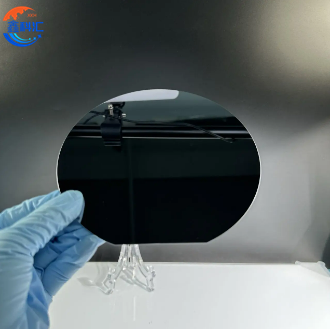

Mewn prosesau silicon CMOS, mae twf epitacsial (EPI) ar y swbstrad wafer yn gam proses hanfodol.

1、Gwella ansawdd crisial

Diffygion ac amhureddau cychwynnol y swbstrad: Yn ystod y broses weithgynhyrchu, gall fod gan y swbstrad wafer rai diffygion ac amhureddau. Gall twf yr haen epitacsial gynhyrchu haen silicon monogrisialog o ansawdd uchel gyda chrynodiadau isel o ddiffygion ac amhureddau ar y swbstrad, sy'n hanfodol ar gyfer cynhyrchu dyfeisiau wedi hynny.

Strwythur grisial unffurf: Mae twf epitacsial yn sicrhau strwythur grisial mwy unffurf, gan leihau effaith ffiniau grawn a diffygion yn y deunydd swbstrad, a thrwy hynny wella ansawdd grisial cyffredinol y wafer.

2, gwella perfformiad trydanol.

Optimeiddio nodweddion dyfeisiau: Drwy dyfu haen epitacsial ar y swbstrad, gellir rheoli crynodiad a math y dopio silicon yn fanwl gywir, gan optimeiddio perfformiad trydanol y ddyfais. Er enghraifft, gellir addasu dopio'r haen epitacsial yn fân i reoli foltedd trothwy MOSFETs a pharamedrau trydanol eraill.

Lleihau cerrynt gollyngiadau: Mae gan haen epitacsial o ansawdd uchel ddwysedd diffygion is, sy'n helpu i leihau cerrynt gollyngiadau mewn dyfeisiau, a thrwy hynny wella perfformiad a dibynadwyedd dyfeisiau.

3, gwella perfformiad trydanol.

Lleihau Maint y Nodweddion: Mewn nodau proses llai (megis 7nm, 5nm), mae maint nodweddion dyfeisiau'n parhau i grebachu, gan olygu bod angen deunyddiau mwy mireinio ac o ansawdd uchel. Gall technoleg twf epitacsial fodloni'r gofynion hyn, gan gefnogi gweithgynhyrchu cylchedau integredig perfformiad uchel a dwysedd uchel.

Gwella Foltedd Dadansoddi: Gellir dylunio haenau epitacsial gyda folteddau dadansoddi uwch, sy'n hanfodol ar gyfer gweithgynhyrchu dyfeisiau pŵer uchel a foltedd uchel. Er enghraifft, mewn dyfeisiau pŵer, gall haenau epitacsial wella foltedd dadansoddi'r ddyfais, gan gynyddu'r ystod weithredu ddiogel.

4、Cydnawsedd Prosesau a Strwythurau Aml-haen

Strwythurau Amlhaenog: Mae technoleg twf epitacsial yn caniatáu twf strwythurau amlhaenog ar swbstradau, gyda gwahanol haenau â chrynodiadau a mathau dopio amrywiol. Mae hyn yn fuddiol iawn ar gyfer gweithgynhyrchu dyfeisiau CMOS cymhleth a galluogi integreiddio tri dimensiwn.

Cydnawsedd: Mae'r broses twf epitacsial yn gydnaws iawn â phrosesau gweithgynhyrchu CMOS presennol, gan ei gwneud hi'n hawdd ei hintegreiddio i lifau gwaith gweithgynhyrchu cyfredol heb yr angen am addasiadau sylweddol i'r llinellau proses.

Crynodeb: Nod pennaf y defnydd o dwf epitacsial mewn prosesau silicon CMOS yw gwella ansawdd crisial wafer, optimeiddio perfformiad trydanol dyfeisiau, cefnogi nodau proses uwch, a bodloni gofynion gweithgynhyrchu cylchedau integredig perfformiad uchel a dwysedd uchel. Mae technoleg twf epitacsial yn caniatáu rheolaeth fanwl gywir ar ddopio a strwythur deunyddiau, gan wella perfformiad a dibynadwyedd cyffredinol dyfeisiau.

Amser postio: Hydref-16-2024